# PC CARD STANDARD

Volume 7 PC Card ATA Specification

| Date PC Card ATA<br>Specification Version |      | PC Card Standard<br>Release    | Revisions                                                                                                         |

|-------------------------------------------|------|--------------------------------|-------------------------------------------------------------------------------------------------------------------|

| 07/92                                     | 1.0  |                                | Initial release as independent specification                                                                      |

| 11/92                                     | 1.01 | PCMCIA 2.01                    | Editorial corrections                                                                                             |

| 07/93                                     | 1.02 | PCMCIA 2.1/JEIDA 4.2           | Editorial corrections                                                                                             |

| 02/95                                     | 5.0  | February 1995 (5.0)<br>Release | Reformatted                                                                                                       |

| 03/95                                     | N/A  | March 1995 (5.01) Update       | None                                                                                                              |

| 05/95                                     | N/A  | May 1995 (5.02) Update         | None                                                                                                              |

| 11/95                                     | N/A  | November 1995 (5.1)<br>Update  | None                                                                                                              |

| 05/96                                     | N/A  | May 1996 (5.2) Update          | None                                                                                                              |

| 03/97                                     | 6.0  | 6.0 Release                    | None                                                                                                              |

| 04/98                                     | 6.1  | 6.1 Update                     | Correction for CISTPL_FUNCE                                                                                       |

| 02/99                                     | 7.0  | 7.0 Release                    | None                                                                                                              |

| 03/00                                     | 7.1  | 7.1 Update                     | None                                                                                                              |

| 11/00                                     | 7.2  | 7.2 Update                     | Editorial corrections to bring the PC Card ATA<br>Specification into line with current ANSI ATA<br>Specifications |

| 04/01                                     | 8.0  | 8.0 Release                    | Changed to PC Card Standard Volume Number 7<br>(was Volume Number 8)                                              |

# **REVISION HISTORY**

#### ©2001 PCMCIA/JEITA

All rights reserved.

No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, mechanical, electronic, photocopying, recording or otherwise, without prior written permission of PCMCIA and JEITA. Published in the United States of America.

# **CONTENTS**

| 1. | Introduction                                                                     | 1                                |

|----|----------------------------------------------------------------------------------|----------------------------------|

|    | 1.1 Purpose                                                                      | 1                                |

|    | 1.2 Scope                                                                        | 1                                |

|    | 1.3 Related Documents                                                            | 1                                |

|    | 1.4 Conventions                                                                  | 2                                |

|    | 1.4.1 Signal Naming                                                              |                                  |

|    | 1.4.2 Numeric Representation                                                     |                                  |

|    | 1.4.3 Bit Action Representation                                                  | 2                                |

| 2. | Overview                                                                         | 3                                |

|    | 2.1 Feature Summary                                                              |                                  |

|    | 2.2 Differences Between PC Card ATA and ATA                                      | 3                                |

| 3. | Electrical Interface                                                             | 7                                |

|    | 3.1 Pin Assignment Table                                                         |                                  |

|    | 3.2 Reset Conditions                                                             | 10                               |

|    | 3.3 READY Signal and RREADY Bit                                                  | 10                               |

|    | 3.4 Interrupt Request: IREQ#                                                     | 11                               |

| 4  | ATA Specific Register Definitions                                                | 13                               |

| 1. | 4.1 PC Card ATA Drive Register and Protocol Definitions                          |                                  |

|    | 4.2 ATA Registers                                                                |                                  |

|    | 4.2 ATA Registers                                                                |                                  |

|    | 4.2.2 Error Register                                                             |                                  |

|    | 4.2.3 Feature Register                                                           |                                  |

|    | 4.2.4 Sector Count Register                                                      | 15                               |

|    | 4.2.5 Sector Number Register                                                     | 15                               |

|    |                                                                                  |                                  |

|    | 4.2.6 Cylinder Low Register                                                      |                                  |

|    | 4.2.7 Cylinder High Register                                                     | 16                               |

|    | <ul><li>4.2.7 Cylinder High Register</li><li>4.2.8 Drive/Head Register</li></ul> | 16<br>17                         |

|    | <ul> <li>4.2.7 Cylinder High Register</li></ul>                                  | 16<br>17<br>17                   |

|    | <ul><li>4.2.7 Cylinder High Register</li><li>4.2.8 Drive/Head Register</li></ul> | 16<br>17<br>17<br>18             |

|    | <ul> <li>4.2.7 Cylinder High Register</li></ul>                                  | 16<br>17<br>17<br>18<br>18       |

|    | <ul> <li>4.2.7 Cylinder High Register</li></ul>                                  | 16<br>17<br>17<br>18<br>18<br>19 |

|    | <ul> <li>4.2.7 Cylinder High Register</li></ul>                                  |                                  |

|    | 4.3.2 Memory Mapped Addressing                                                                                                                                                |              |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| 5. | Software Interface                                                                                                                                                            | 23           |

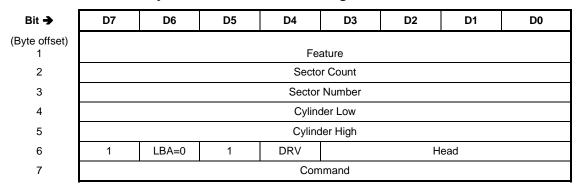

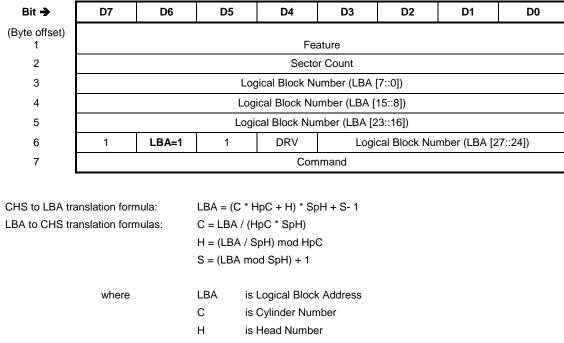

|    | <ul> <li>5.1 ATA Command Block.</li> <li>5.1.1 ATA Command Block for Cylinder-Head-Sector Addressing</li> <li>5.1.2 ATA Command Block for Logical Block Addressing</li> </ul> | 23<br>       |

|    | 5.2 Command Descriptions                                                                                                                                                      | 24           |

| 6. | Interface Protocol                                                                                                                                                            | 25           |

|    | <ul> <li>6.1 ATA Soft Reset</li></ul>                                                                                                                                         | 25<br>       |

| 7. | PC Card Specific Considerations                                                                                                                                               | 29           |

|    | 7.1 Card Configuration Registers                                                                                                                                              | 29           |

|    | 7.2 Card Removal, Insertion and Change Detection                                                                                                                              | 29           |

| 8. | Appendix A: Implementation Notes                                                                                                                                              | 31           |

|    | 8.1 Special Handling of I/O Ports 3F7H and 377H                                                                                                                               | 31           |

| 9. | Appendix B: Card Information Structure                                                                                                                                        | 33           |

|    | 9.1 Card Information Structure                                                                                                                                                | 33           |

|    | 9.2 Function ID Tuple for Disk Function                                                                                                                                       | 33           |

|    | 9.3 Disk Device Interface Function Extension Tuple                                                                                                                            | 34           |

|    | 9.4 PC Card ATA Features Function Extension Tuple                                                                                                                             | 34           |

|    | 9.5 PC Card ATA JEDEC ID's                                                                                                                                                    | 35           |

| 10 | ). Appendix C: CompactFlash and PC Card ATA D                                                                                                                                 | ifferences37 |

|    | 10.1     CompactFlash Differences                                                                                                                                             |              |

| 11 | l. Appendix D: True IDE Mode                                                                                                                                                  | 39           |

|    | 11.1 True IDE mode                                                                                                                                                            |              |

# TABLES

## **1.** INTRODUCTION

## 1.1 Purpose

This specification defines the standard method for incorporating an ATA mass storage protocol peripheral on a 16-bit PC Card. This specification supplements the definitions of an ATA mass storage peripheral found in the *ANSI ATA Standard* and the definition of a PC Card found in the *PC Card Standard*.

The PC Card ATA protocol described in this document is compatible with existing PC Card defined socket hardware without any changes or additional pins. PC Card ATA mass storage cards shall be implemented to operate as I/O devices in conformance with *PCMCIA 2.0/JEIDA 4.1* or later. The cards are also permitted to provide a memory mapped configuration compatible with socket hardware defined in *PCMCIA 1.0/JEIDA 4.0*.

This document describes the electrical and software interfaces for a PC Card ATA mass storage card. The standard address mappings for a PC Card ATA mass storage card are also described.

## 1.2 Scope

This document is intended to be used together with the *PC Card Standard* and the *ANSI ATA Standard*. It is intended to highlight those areas of implementation in which the *PC Card Standard* and the *ANSI ATA Standard* conflict. In addition, an indication is made of areas within the *ANSI ATA Standard* which are modified for operation in a PC Card environment. Both mandatory and optional specifications are presented.

In the event of a conflict between one of the base documents (*PC Card Standard* or *ANSI ATA Standard*) and this document, the interpretation of this document shall prevail if and only if this document specifies that a conflict exists between the documents.

This document also highlights differences between CompactFlash and PC Card ATA.

Note: CompactFlash is a registered trademark of the CompactFlash Association.

## **1.3 Related Documents**

There are related documents upon which this document is based and which are required for understanding and implementing a PC Card ATA mass storage peripheral.

PC Card Standard Release 8.0 (April 2001), PCMCIA/JEITA

Volume 1. Overview and Glossary

Volume 2. Electrical Specification

Volume 3. Physical Specification

Volume 4. Metaformat Specification

Volume 5. Card Services Specification

Volume 6. Socket Services Specification

Volume 7. PC Card ATA Specification

Volume 8. PC Card Host Systems Specification

Volume 9. Guidelines

Volume 10. Media Storage Formats Specification

Volume 11. XIP Specification

The following are referred to as the "ANSI ATA Standard": AT Attachment For Disk Drives, Document Number X3.221-1994, ANSI AT Attachment – 2 Interface (with Extensions) (ATA-2), ANSI AT Attachment – 3 Interface (ATA-3), ANSI AT Attachment – 4 Interface (ATA-4), ANSI

Note: Since this document describes the PC Card bus interface to an ATA device, it is expected that future AT Attachment specifications will be compatible with this *PC Card ATA Standard*.

CompactFlash Specification, CompactFlash Association

## **1.4 Conventions**

This section is intended to give general descriptions of notational conventions used in this document.

See the *Overview and Glossary* volume for an extensive set of definitions of terms found in the *PC Card ATA Specification*. In many cases, more detailed information about these terms may be found in the *PC Card Standard* or one of the *ANSI ATA Standards*. These documents should be consulted for more detailed and precise definitions of terms.

## 1.4.1 Signal Naming

All signals are named with respect to their asserted state as follows:

- a) Each signal which is not a logic signal, such as **Vcc**, has a name which does not end with a "#" character.

- b) Each logic signal whose name does not end with a "#" character has logic high as the asserted state and logic low as the negated state.

- c) Each logic signal whose name ends with a "#" character has logic low as the asserted state and logic high as the negated state.

## 1.4.2 Numeric Representation

Numbers are expressed as follows:

- a) Individual bits are expressed as "0" for zero, "1" for one, or "X" for don't care.

- b) Groups of bits (fields) are expressed in hexadecimal number which begin with a decimal digit and are followed by an "H". Each digit represents 4 bits and ranges from 0H to 9H and AH to FH for 0 to 15 (decimal) with an "X" being used for don't care. The number of bits in the field determines how many bits in the hexadecimal number are significant.

## 1.4.3 Bit Action Representation

Bits of a register are said to be set when they are made equal to "1" and to be cleared when they are made equal to "0."

## 2. OVERVIEW

This document details the requirements and considerations in implementing an ATA protocol mass storage peripheral within the PC Card environment.

The ATA protocol is followed except where the PC Card interface imposes conflicting constraints to traditional ATA host bus adapters. This document describes how the ATA protocol maps onto the PC Card interface. It resolves and clarifies the enhancements and restrictions which result from the use of the PC Card interface with the ATA protocol.

Mandatory support is provided for the AT BIOS ATA Control Block and Command Block registers at 1F0H-1F7H, 3F6H-3F7H or 170H-177H, 376H-377H typically using IRQ14. These I/O register assignments are usable with pre-existing AT BIOS Device Drivers. Mandatory support is also provided for locating the I/O ports in a contiguous I/O window of at least 16 bytes which is decoded for the PC Card by the socket. PC Cards can also be built that may be placed by the system in a 2 KB host memory space by a dedicated driver.

The use of a well known, dominant, standard interface in mobile computers guarantees system vendors an interface which remains stable over the coming generations of silicon and rotating mass storage devices.

## 2.1 Feature Summary

- a) The PC Card ATA protocol is based on the widely accepted and established ATA protocol which is an accepted standard for disk drives in mobile computers. It is also based on the PC Card interface standard which is the peripheral interface for mobile computing.

- b) The ATA protocol is very familiar to both system designers and software developers.

- c) This protocol allows PC Card ATA mass storage cards to be "plug and play" in many existing systems and applications.

- d) The protocol is compatible with existing ATA software.

- e) The protocol fits easily into the architecture of desktop PCs as well as mobile computers.

- f) Allows a CompactFlash adapter to operate a CompactFlash card in a PC Card slot.

## 2.2 Differences Between PC Card ATA and ATA

- a) The Diagnostic command runs only on the card which is addressed by the Drive/Head register when the Diagnostic Command is issued. This is because the PC Card interface does not provide for direct inter-drive communication (i.e., the ATA **PDIAG** and **DASP** signals). Therefore, unlike ATA, it is not possible when using the PC Card interface for Drive 0 to report status for both drives.

- b) The *PC Card ATA Specification* provides for two cards at a single address through the Twin Card option in CIS (See the *Metaformat Specification*) and card enumeration using the Socket and Copy register (See the *Electrical Specification*). The *ANSI ATA Standard* provides card enumeration using a jumper or cable strap. The ATA signals PDIAG- and DASP- are not implemented in the *PC Card ATA Specification*.

- c) The *PC Card ATA Specification* provides a **READY** signal which can be used to prevent the host from accessing the card's registers before the card is available following card detected power-on,

hardware reset, or PC Card soft reset. With an appropriate socket, this signal is also used while a card is configured in the memory mapped mode to provide a socket generated host interrupt on the transition to ready.

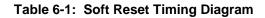

- d) The *PC Card ATA Specification* provides an ATA Soft Reset protocol described in Section 6.1, ATA Soft Reset.

- e) The implementation of the Index bit, IDX, in the Status register and the Alternate Status register is optional. If implemented, it shall be implemented as defined in the *ANSI ATA Standard*.

- f) I/O ports 3F7H and 377H in the Primary and Secondary I/O mapped modes have a potential conflict with a floppy disk controller installed in the host. There is a potential problem with the protocol described in the *ANSI ATA Standard* for sharing the Drive Address register with a floppy disk controller when either the ATA peripheral or the floppy disk controller are accessed through the PC Card interface.

Refer to Appendix B for possible methods to avoid this problem.

g) The PC Card interface permits the host to access the ATA registers in more alternative ways than the traditional ATA host bus adapter allows. These alternatives arise from the presence of two card enable signals, **CE[2::1]**#, in addition to address line **A0**.

The PC Card interface allows access to registers at odd addresses with two different methods.

a) When address line **A0** is 1 (logic high), if **CE1#** is asserted and **CE2#** is negated during the read or write cycle, then the byte of data at the odd address is transferred on signals **D[7::0]** of the Data Bus.

b) Regardless of the state of address line **A0** and of the state of **CE1#**, if **CE2#** is asserted the byte of data at the odd address is transferred on signals **D[15::8]** of the Data Bus. If **CE1#** is also asserted, then a 16-bit word is accessed. If **CE1#** is negated, then only the byte at the odd address is accessed.

A sixteen bit word of data is accessed when both **CE[2::1]**# are active, regardless of the state of **A0**.

h) I/O accesses are constrained at the PC Card interface as follows:

a) The host shall perform all word (16-bit) I/O accesses with A0 = 0.

b) During a host's word access attempt, if a card asserts **IOIS16#** in response to the address on the bus then the host system is permitted to transfer 16 bits of data to the card in a single cycle, otherwise, the host system shall perform two 8-bit cycles: even byte then odd byte.

i) The *ANSI ATA Standard* specifies that the Data register is two bytes wide and is located at offset, or relative address zero while the Error and Feature registers are one byte wide and are located at offset one within the ATA registers. This results in an overlap of the address spaces between the Data register and Error-Feature register combination.

Some host architectures do not permit word and byte registers to overlap. To permit those hosts to access all the registers of the PC Card ATA mass storage card, the *PC Card ATA Specification* provides a non-overlapping duplicate copy of each of these registers in the Memory Mapped and Contiguous I/O mapped configurations. Within the 16 byte space occupied by the ATA registers in these configurations, the duplicate data register is located at offset 8H while the duplicate Error and Feature registers are located at offset 0DH.

Refer to Section 4.2.13, Duplicate Data, Error and Feature Registers, for more information about the duplicate copies of these registers.

- j) Implementation of the Identify Drive Command is mandatory in the PC Card Standard, but optional in some versions of the *ANSI ATA Standard*.

- k) Eight and 16-bit data accesses are mandatory in PC Card -- only 16-bit accesses are specified in some *ANSI ATA Standards*.

- l) IOCS16# (IOIS16#) is obsolete in some ANSI ATA Standards.

- m) The Drive Address register is obsolete in some ANSI ATA Standards.

# 3. ELECTRICAL INTERFACE

A PC Card ATA mass storage card uses the PC Card electrical interface. A subset of the entire PC Card interface is sufficient for PC Card ATA implementation. Both mandatory and optional signals are given in this section. Special consideration is given to some signals whose definition is expanded when used in the PC Card ATA mass storage card.

## 3.1 Pin Assignment Table

The following is the recommended pin assignment table for implementing PC Card ATA protocol. The mandatory Interface signals are required for using the card in the mandatory card decoded and host decoded I/O spaces.

| Pin # | PC Card<br>Memory<br>Interface Signal | PC Card I/O<br>Interface Signal | PC Card ATA<br>Mandatory<br>Signal | PC Card ATA<br>Optional Signal | Notes <sup>7</sup> |

|-------|---------------------------------------|---------------------------------|------------------------------------|--------------------------------|--------------------|

| 1     | GND                                   | GND                             | GND                                |                                |                    |

| 2     | D3                                    | D3                              | D3                                 |                                |                    |

| 3     | D4                                    | D4                              | D4                                 |                                |                    |

| 4     | D5                                    | D5                              | D5                                 |                                |                    |

| 5     | D6                                    | D6                              | D6                                 |                                |                    |

| 6     | D7                                    | D7                              | D7                                 |                                |                    |

| 7     | CE1#                                  | CE1#                            | CE1#                               |                                |                    |

| 8     | A10                                   | A10                             |                                    | A10                            | 1                  |

| 9     | OE#                                   | OE#                             | OE#                                |                                |                    |

| 10    | A11                                   | A11                             |                                    | A11                            | 2                  |

| 11    | A9                                    | A9                              | A9                                 |                                |                    |

| 12    | A8                                    | A8                              | A8                                 |                                |                    |

| 13    | A13                                   | A13                             |                                    | A13                            | 2                  |

| 14    | A14                                   | A14                             |                                    | A14                            | 2                  |

| 15    | WE#                                   | WE#                             | WE#                                |                                |                    |

| 16    | READY                                 | IREQ#                           | READY:<br>IREQ#                    |                                | 6                  |

| 17    | Vcc                                   | Vcc                             | Vcc                                |                                |                    |

| 18    | Vpp1                                  | Vpp1                            | Vpp1 or<br>No Connect              |                                | 3                  |

| 19    | A16                                   | A16                             |                                    | A16                            | 2                  |

| 20    | A15                                   | A15                             |                                    | A15                            | 2                  |

| 21    | A12                                   | A12                             |                                    | A12                            | 2                  |

| 22    | A7                                    | A7                              | A7                                 |                                |                    |

| 23    | A6                                    | A6                              | A6                                 |                                |                    |

| 24    | A5                                    | A5                              | A5                                 |                                |                    |

Table 3-1: PC Card ATA Signal Names and Pin Assignment

# Table 3-1: PC Card ATA Signal Names and Pin Assignment (Continued)

| Pin # | PC Card<br>Memory<br>Interface Signal | PC Card I/O<br>Interface Signal | PC Card ATA<br>Mandatory<br>Signal | PC Card ATA<br>Optional Signal | Notes <sup>7</sup> |

|-------|---------------------------------------|---------------------------------|------------------------------------|--------------------------------|--------------------|

| 25    | A4                                    | A4                              | A4                                 |                                |                    |

| 26    | A3                                    | A3                              | A3                                 |                                |                    |

| 27    | A2                                    | A2                              | A2                                 |                                |                    |

| 28    | A1                                    | A1                              | A1                                 |                                |                    |

| 29    | A0                                    | A0                              | A0                                 |                                |                    |

| 30    | D0                                    | D0                              | D0                                 |                                |                    |

| 31    | D1                                    | D1                              | D1                                 |                                |                    |

| 32    | D2                                    | D2                              | D2                                 |                                |                    |

| 33    | WP                                    | IOIS16#                         | WP:<br>IOIS16#                     |                                |                    |

| 34    | GND                                   | GND                             | GND                                |                                |                    |

| 35    | GND                                   | GND                             | GND                                |                                |                    |

| 36    | CD1#                                  | CD1#                            | CD1#                               |                                |                    |

| 37    | D11                                   | D11                             | D11                                |                                |                    |

| 38    | D12                                   | D12                             | D12                                |                                |                    |

| 39    | D13                                   | D13                             | D13                                |                                |                    |

| 40    | D14                                   | D14                             | D14                                |                                |                    |

| 41    | D15                                   | D15                             | D15                                |                                |                    |

| 42    | CE2#                                  | CE2#                            | CE2#                               |                                |                    |

| 43    | VS1#                                  | VS1#                            | VS1#                               |                                |                    |

| 44    |                                       | IORD#                           | IORD#                              |                                |                    |

| 45    |                                       | IOWR#                           | IOWR#                              |                                |                    |

| 46    | A17                                   | A17                             |                                    | A17                            | 2                  |

| 47    | A18                                   | A18                             |                                    | A18                            | 2                  |

| 48    | A19                                   | A19                             |                                    | A19                            | 2                  |

| 49    | A20                                   | A20                             |                                    | A20                            | 2                  |

| 50    | A21                                   | A21                             |                                    | A21                            | 2                  |

| 51    | Vcc                                   | Vcc                             | Vcc                                |                                |                    |

| 52    | Vpp2                                  | Vpp2                            | Vpp2 or No<br>Connect              |                                | 3                  |

| 53    | A22                                   | A22                             |                                    | A22                            | 2                  |

| 54    | A23                                   | A23                             |                                    | A23                            | 2                  |

| 55    | A24                                   | A24                             |                                    | A24                            | 2                  |

| 56    | A25                                   | A25                             |                                    | A25                            | 2                  |

| 57    | VS2#                                  | VS2#                            | VS2#                               |                                |                    |

| 58    | RESET                                 | RESET                           | RESET                              |                                |                    |

| Pin # | PC Card<br>Memory<br>Interface Signal | PC Card I/O<br>Interface Signal | PC Card ATA<br>Mandatory<br>Signal   | PC Card ATA<br>Optional Signal | Notes <sup>7</sup> |

|-------|---------------------------------------|---------------------------------|--------------------------------------|--------------------------------|--------------------|

| 59    | WAIT#                                 | WAIT#                           | WAIT#                                |                                |                    |

| 60    |                                       | INPACK#                         | INPACK#                              |                                |                    |

| 61    | REG#                                  | REG#                            | REG#                                 |                                |                    |

| 62    | BVD2                                  | SPKR#                           | Logic High<br>unless BVD2:<br>SPKR#  | BVD2:<br>SPKR#                 | 4                  |

| 63    | BVD1                                  | STSCHG#                         | Logic High<br>unless BVD:<br>STSCHG# | BVD1:<br>STSCHG#               | 5                  |

| 64    | D8                                    | D8                              | D8                                   |                                |                    |

| 65    | D9                                    | D9                              | D9                                   |                                |                    |

| 66    | D10                                   | D10                             | D10                                  |                                |                    |

| 67    | CD2#                                  | CD2#                            | CD2#                                 |                                |                    |

| 68    | GND                                   | GND                             | GND                                  |                                |                    |

# Table 3-1: PC Card ATA Signal Names and Pin Assignment (Continued)

#### NOTES:

Signal names in the PC Card ATA columns indicate dual function signals by listing the Memory Interfaced function, followed by a colon (:), and then the I/O Interfaced function of the signal. Signals in the PC Card ATA Optional column may be mandatory for particular features which the card vendor may choose to implement. The use of optional signals is described in the following numbered notes.

- 1. Address line **A10** is mandatory if Memory Mapped addressing is supported. Otherwise, **A10** is permitted to be implemented at the discretion of the card vendor.

- 2. Address lines A[25::11] are permitted to be implemented at the discretion of the card vendor.

- 3. The use of the **Vpp[2::1]** supplies is optional. If they are used, it is recommended that the card vendor select +12 V as the **Vpp** value. A card which does not require any **Vpp** supply, shall leave both **Vpp** pins unconnected at the card.

The **Vpp[2::1]** supplies shall not be connected to each other on the card. When only one supply is required, it is recommended that **Vpp1** be used.

At power up, the host shall provide at least minimal current at Vcc Volts on both Vpp[2::1].

- 4. The I/O signal SPKR# is optional. If the function is not implemented, this pin shall be held at logic high (negated) by the card. The memory signal BVD2 shall be held high unless it is indicating the state of a battery on the card.

- 5. The I/O signal STSCHG# is optional, however it shall be implemented if both the Function Configuration and Status register and the Pin Replacement register are implemented. If the function is not implemented, this pin shall be held high (negated) by the card. The memory signal BVD1 shall be held high unless it is indicating the state of a battery on the card.

- 6. The negated state of the **READY** signal shall be interpreted to be the Busy state of the signal. See **3.3** *READY Signal and RREADY Bit*, for additional information on the **READY** signal.

- 7. All signals shown in the PC Card ATA mandatory column shall be implemented by all PC Card ATA mass storage cards.

## 3.2 Reset Conditions

There are four distinct reset conditions associated with the PC Card ATA mass storage card. They are as follows:

- a) Card detected Power-On Reset;

- b) Host generated PC Card Hardware Reset using the Reset signal;

- c) Host initiated PC Card Soft Reset using SRESET bit in the Configuration Option register;

- d) ATA Soft Reset using the SRST bit in the ATA Device Control register.

The host should always accompany a card Power-On event with a host generated hardware reset as described in the Power-Up and Power-Down section of the *Electrical Specification*.

Power-On, PC Card Hardware Reset and PC Card Soft Reset all clear the Configuration Option register (configuration index value of 0H) as described in the **RESET** signal description in the *Electrical Specification* and cause the card to perform the ATA Hard Reset protocol.

The PC Card Soft Reset has the same effect as the Host generated hardware reset with the exception that the PC Card Software Reset bit itself is not cleared by the assertion of Soft Reset as described in the Configuration Option register section of the *Electrical Specification*.

The ATA Soft Reset protocol does not affect the card's PC Card configuration, but does perform ATA Soft Reset protocol as specified in the *ANSI ATA Standard* and modified in Section 6.1 ATA Soft Reset, of this document.

## 3.3 READY Signal and RREADY Bit

The **READY** signal is available while the card is configured to use the Memory Interface. This signal is unavailable and is replaced by the interrupt request signal, **IREQ#**, while the card is configured to use the I/O interface. The **READY** signal is negated when the card is in the Busy condition.

If the Pin Replacement register is implemented on the card, the RREADY bit in that register is cleared when the card is busy and set when the card is ready.

The card shall be Busy under the following conditions:

- a) From Power-On until the card is ready to be accessed.

- b) From PC Card Hardware Reset until the card is ready to be accessed.

- c) From PC Card Soft Reset until the card is ready to be accessed.

- d) If a card supports the PC Card Power-Down bit in the Configuration and Status register, then from a change in the PC Card Power-Down bit until the card has completed the requested Power-Down or Power-Up operation.

- e) While the card is in a Memory interface configuration, whenever the BSY bit in the ATA Status register is set.

## 3.4 Interrupt Request: IREQ#

The interrupt request signal from the card (**IREQ#**) is available only when the card is configured to use the PC Card I/O interface. The handling of this signal is slightly different from the handling of the ATA interrupt request signal, **IRQ**.

The polarity of the PC Card **IREQ**# signal is opposite to that of the ATA **IRQ** signal. The PC Card **IREQ**# signal has a mandatory PC Card level mode interrupt and an optional PC Card pulse mode interrupt. The pulse mode interrupt is designed to allow sharing of interrupts in hosts which use an ISA compatible system bus between the PC Card socket and the host's CPU. To take advantage of a PC Card pulse mode interrupt, the host socket must be able to pass the interrupt request signal without inversion from the PC Card to the internal ISA bus and to drive the ISA bus **IRQn** signal with an open collector driver.

When the nIEN bit in the ATA Device Control register is set, the PC Card ATA mass storage card shall not assert the **IREQ#** signal. This is in contrast to the **ANSI ATA Standard** which specifies that the ATA interrupt request signal, **IRQ**, is placed in high impedance during these times.

# 4. ATA SPECIFIC REGISTER DEFINITIONS

## 4.1 PC Card ATA Drive Register and Protocol Definitions

PC Card ATA mass storage cards can be configured as a high performance I/O device through standard I/O address spaces: 1F0H-1F7H, 3F6H-3F7H (primary); 170H-177H, 376H-377H (secondary) and IRQ 14 or anywhere in the I/O space or memory space requiring a dedicated driver. The communications to and from the drive is performed using the ATA Command Block which provides all the necessary control and status information. The PC Card interface connects peripherals to the host using four register mapping methods. Table 4-1: Standard Configurations is a description of these methods:

| Config<br>Index | I/O or<br>Memory | Address<br>A[10::0]                                            | Drive<br>Number | Socket &<br>Copy | Mandatory or<br>Optional | Description                              |

|-----------------|------------------|----------------------------------------------------------------|-----------------|------------------|--------------------------|------------------------------------------|

| 0н <sup>1</sup> | Memory           | 0н - 0Fн,<br>400н - 7FFн                                       | 0               | X000XXXX         | Optional                 | Memory<br>Mapped                         |

| 1H <sup>1</sup> | I/O              | ХХ0н - ХХГн                                                    | 0               | X000XXXX         | Mandatory                | I/O Mapped 16<br>Contiguous<br>Registers |

| 2H1             | I/O              | 1F0н -1F7н,<br>3F6н - 3F7н<br><br>5F0н - 5F7н,<br>7F6н - 7F7н  | 0               | X000XXXX         | Mandatory                | Primary I/O<br>Mapped Drive 0            |

| 2H <sup>1</sup> | I/O              | 1F0н -1F7н,<br>3F6н- 3F7н<br><br>5F0н - 5F7н,<br>7F6н - 7F7н   | 1               | X001XXXX         | Optional                 | Primary I/O<br>Mapped Drive 1            |

| 3н1             | I/O              | 170н - 177н,<br>376н - 377н<br><br>570н - 577н,<br>776н - 777н | 0               | X000XXXX         | Mandatory                | Secondary I/O<br>Mapped Drive 0          |

| 3н1             | I/O              | 170н - 177н,<br>376н - 377н<br><br>570н - 577н,<br>776н - 777н | 1               | X001XXXX         | Optional                 | Secondary I/O<br>Mapped Drive 1          |

#### Table 4-1: Standard Configurations

NOTES:

1. The configuration indices indicated here are for example only for PC Card ATA. (These indices are required for CompactFlash cards).

The host selects the card's register mapping configuration by writing the Function Configuration Index value to the least significant 6 bits of the card's Configuration Option register. The actual configuration index values used by a card are vendor specific and are reported to the host using the Configuration Table Entry tuples. However, configuration 0H shall always select the PC Card Memory-Only interface.

## 4.2 ATA Registers

The ATA registers are the registers which are provided on the card specifically to implement the ATA aspects of the PC Card ATA protocol. The first eight registers and duplicates are referred to as the ATA Command Block.

In accordance with the *PC Card Standard* each of the registers below which is located at an odd address may be accessed using either data bus lines **D**[15::8] or using data bus lines **D**[7::0]. Refer to Section 2.2, Differences Between PC Card ATA and ATA, or to the *Electrical Specification* for more information.

## 4.2.1 Data Register

The Data register is a 16-bit register which is used to transfer data blocks between the card data buffer and the host. Data may be transferred by either a series of word accesses to the Data register or a series of byte accesses to the Data register. The *ANSI ATA Standard* Signal Descriptions and Set Features Command sections specify under what conditions word and byte accesses from the host are appropriate to access this register.

#### Table 4-2: Data Register

Refer to the *ANSI ATA Standard* for detailed information about this register. Refer also to Section 4.2.13, Duplicate Data, Error and Feature Registers, for additional information about the Data register, the Duplicate Data registers, and the interactions between the Data register and the Error or Feature register.

Some *ANSI ATA Standards* define this as a 16-bit-only register. PC Card ATA requires this register to be accessible as 8 or 16 bits.

## 4.2.2 Error Register

This register contains additional information about the source of an error which has occurred in processing of the preceding command. This register should be checked by the host when bit 0 (ERR) in the Status register is set. The Error register is a read only register. When writing to the address of the Error register, the Feature register is written.

| Table 4-3: | Error | Register |

|------------|-------|----------|

|------------|-------|----------|

| D7  | D6  | D5 | D4   | D3  | D2   | D1    | D0   |

|-----|-----|----|------|-----|------|-------|------|

| BBK | UNC | MC | IDNF | MCR | ABRT | TKNOF | AMNF |

All bits in this register are defined in the *ANSI ATA Standard*. Refer to the *ANSI ATA Standard* for a detailed description of this register. Refer also to Section 4.2.13, Duplicate Data, Error and Feature

Registers, for additional information about the Error register, the Duplicate Error register, and the interactions between the Data register and the Error register.

Note: The BBK bit is reserved in some ANSI ATA Standards.

## 4.2.3 Feature Register

This register is written by the host to provide command specific information to the drive regarding features of the drive which the host wishes to utilize. The Feature register is a write only register. When reading from the address of the Feature register, the Error register is read. This register may be ignored by some drives.

#### Table 4-4: Feature Register

|   | D7 | D6 | D5 | D4     | D3     | D2 | D1 | D0 |

|---|----|----|----|--------|--------|----|----|----|

| ľ |    |    |    | Featur | e Byte |    |    |    |

Refer to the *ANSI ATA Standard* for a detailed description of this register. Refer also to Section 4.2.13: Duplicate Data, Error and Feature Registers, for additional information about the Feature register, the Duplicate Feature register, and the interactions between the Data registers and the Feature register.

## 4.2.4 Sector Count Register

This register is written by the host with the number of sectors or blocks to be processed in the subsequent command. After the command is complete, the host may read this register to obtain the count of sectors left unprocessed by the command.

#### Table 4-5: Sector Count Register

| D7           | D6 | D5 | D4 | D3 | D2 | D1 | D0 |  |

|--------------|----|----|----|----|----|----|----|--|

| Sector Count |    |    |    |    |    |    |    |  |

Refer to the ANSI ATA Standard for a detailed description of this register.

### 4.2.5 Sector Number Register

This register is written by the host with the starting sector number to be used in the subsequent Cylinder-Head-Sector command. After the command is complete, the host may read the final sector number from this register. When logical block addressing is used, this register is written by the host with bits 7 to 0 of the starting logical block number and contains bits 7 to 0 of the final logical block number after the command is complete.

#### Table 4-6: Sector Number Register

| D7 D6 D5 D4 D3 D2 D1 D0 |                                |  |      |                 |                  |        |  | D0 |

|-------------------------|--------------------------------|--|------|-----------------|------------------|--------|--|----|

|                         | Sector Number (CHS Addressing) |  |      |                 |                  |        |  |    |

|                         |                                |  | Logi | ical Block Numl | ber bits (LBA [7 | '::0]) |  |    |

Refer to the ANSI ATA Standard for a detailed description of this register.

## 4.2.6 Cylinder Low Register

This register is written by the host with the low-order byte of the starting cylinder address to be used in the subsequent Cylinder-Head-Sector command. After the command is complete, the host may read the low-order byte of the final cylinder number from this register. When logical block addressing is used, this register is written by the host with bits 15 to 8 of the starting logical block number and contains bits 15 to 8 of the final logical block number after the command is complete.

| Table 4-7: Cylinder Low Register | Table 4-7: | Cylinder | Low Register |

|----------------------------------|------------|----------|--------------|

|----------------------------------|------------|----------|--------------|

| D7 D6 D5 D4 D3 D2 D1 D0 |                                           |  |  |  |  |  |  |  |

|-------------------------|-------------------------------------------|--|--|--|--|--|--|--|

|                         | Cylinder Number Low Byte (CHS Addressing) |  |  |  |  |  |  |  |

|                         | Logical Block Number bits (LBA [15::8])   |  |  |  |  |  |  |  |

Refer to the ANSI ATA Standard for a detailed description of this register.

## 4.2.7 Cylinder High Register

This register is written by the host with the high-order byte of the starting cylinder address to be used in the subsequent Cylinder-Head-Sector command. After the command is complete, the host may read the high-order byte of the final cylinder number from this register. When logical block addressing is used, this register is written by the host with bits 23 to 16 of the starting logical block number and contains bits 23 to 16 of the final logical block number after the command is complete.

#### Table 4-8: Cylinder High Register

| D7 D6 D5 D4 D3 D2 D1 D0                    |  |  |  |  |  |  |  |  |

|--------------------------------------------|--|--|--|--|--|--|--|--|

| Cylinder Number High Byte (CHS Addressing) |  |  |  |  |  |  |  |  |

| Logical Block Number bits (LBA [23::16])   |  |  |  |  |  |  |  |  |

Refer to the ANSI ATA Standard for a detailed description of this register.

## 4.2.8 Drive/Head Register

The Drive/Head register is used to specify the selected drive of a pair of drives sharing a set of registers. The bits are defined as follows:

| -     |           |                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                            |               |                  |               |  |  |

|-------|-----------|---------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|---------------|------------------|---------------|--|--|

| D7    | D6        | D5                                                                                                            | D5 D4 D3 D2 D1 D0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                            |               |                  |               |  |  |

| 1     | LBA (0)   | 1                                                                                                             | DEV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | HS3                        | HS2           | HS1              | HS0           |  |  |

|       | LBA(1)    |                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | LBA27                      | LBA26         | LBA25            | LBA24         |  |  |

| D'1 7 | 4         | This bit is '1'.                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                            |               |                  |               |  |  |

| Bit 7 | 1         | i nis d                                                                                                       | IT IS 11.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                            |               |                  |               |  |  |

| Bit 6 | LBA       | This bit is '0' for Cylinder-Head-Sector addressing and '1' for Logical Block<br>Addressing.                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                            |               |                  |               |  |  |

| Bit 5 | 1         | This bit is '1'.                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                            |               |                  |               |  |  |

| Bit 4 | DEV       | cleare<br>selecto<br>field of<br>Socke<br>CIS in                                                              | This bit is number of the device which the host has selected. When DEV is cleared, device 0 (card 0) is selected. When DEV is set, drive 1 (card 1) is selected. The card is selected to be Card 0 or to be Card 1 using the "Copy" field of the PC Card Socket and Copy configuration register, if present. If no Socket and Copy configuration register is present on the card, or if the Card's CIS indicates that it does not support Twin-Cards for the selected configuration, then DEV shall be cleared by the host. |                            |               |                  |               |  |  |

| Bit 3 | HS3/LBA27 |                                                                                                               | bit 3 of the hea<br>er in LBA addre                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ad number in Cl<br>essing. | HS addressing | or bit 27 of the | Logical Block |  |  |

| Bit 2 | HS2/LBA26 |                                                                                                               | bit 2 of the hea<br>er in LBA addre                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ad number in Cl<br>essing. | HS addressing | or bit 26 of the | Logical Block |  |  |

| Bit 1 | HS1/LBA25 |                                                                                                               | bit 1 of the hea<br>er in LBA addre                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ad number in Cl<br>essing. | HS addressing | or bit 25 of the | Logical Block |  |  |

| Bit 0 | HS0/LBA24 | This is bit 0 of the head number in CHS addressing or bit 24 of the Logical Block<br>Number in LBA addressing |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                            |               |                  |               |  |  |

Table 4-9: Drive/Head Register

## 4.2.9 Status and Alternate Status Registers

The Status register and the Alternate Status register return the card status when read by the host. Reading the Status register clears a pending interrupt request while reading the Alternate Status register does not.

The Status register and the Alternate Status register are read only registers. When writing to the address of the Status register, the Command register is written. When writing to the address of the Alternate Status register, the Device Control register is written.

The status bits are identified as follows:

| ľ | D7  | D6   | D5 | D4  | D3  | D2   | D1  | D0  |

|---|-----|------|----|-----|-----|------|-----|-----|

|   | BSY | DRDY | DF | DSC | DRQ | CORR | IDX | ERR |

Refer to the *ANSI ATA Standard* for a description of the bits which are described in this register except where the *ANSI ATA Standard* conflicts with the descriptions below.

| Bit 1 | IDX | This bit is optional. If implemented it shall be implemented as described in the <b>ANSI ATA Standard</b> .                                                                                                |

|-------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit 5 | DF  | This bit is used to indicate a device write failure. Devices which require Vpp for write operations should use this bit to signal if the <b>Vpp</b> voltage is out of tolerance when a write is attempted. |

## 4.2.10 Command Register

The Command register contains the command code being sent to the device. Command execution begins immediately after this register is written.

The Command register is a write only register. When reading from the address of the Command register, the Status register is read.

| D7 | D6 | D5 | D4     | D3 | D2 | D1 | D0 |

|----|----|----|--------|----|----|----|----|

|    |    |    | Comman | d  |    |    |    |

### 4.2.11 Device Control Register

This register is used to control the card interrupt request and to issue a soft reset to the card.

The Device Control register is a write only register. When reading from the address of the Device Control register, the Alternate Status register is read.

The bits are defined as follows:

#### Table 4-11: Device Control Register

| D7 | D6 | D5 | D4 | D3 | D2   | D1   | D0 |

|----|----|----|----|----|------|------|----|

| Х  | Х  | Х  | Х  | 1  | SRST | nIEN | 0  |

Refer to the *ANSI ATA Standard* for the general description of the bits which are described in this register except where it conflicts with the descriptions noted below:

| Bit 1 | nIEN | While the card is operating in the memory mapped mode this bit is permitted to be ignored; but see additional requirements in Section 7.1, Card Configuration Registers, for cards which implement the Function Configuration and Status register. |

|-------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       |      | While this bit is cleared, interrupts shall operate as described in the <b>PC Card Standard</b> in response to the events described in the <b>ANSI ATA Standard</b> .                                                                              |

|       |      | While this bit is set, the interrupts on the card shall be disabled. The <b>IREQ#</b> signal in the PC Card I/O interface shall be negated unless the nIEN bit is cleared and an interrupt has been requested.                                     |

| Bit 2 | SRST | The Software Reset bit shall operate generally as described in the <b>ANSI ATA</b><br><b>Standard</b> with the following exceptions:                                                                                                               |

|       |      | Sections of <b>ANSI ATA Standard</b> which refer to the PDIAG- and the DASP-<br>signals are not applicable to PC Card implementations. Section 6.1, ATA Soft<br>Reset, of this document shall define the Soft Reset Function and protocol.         |

## 4.2.12 Drive Address Register

This register is provided for compatibility with the AT disk drive interface. The bits can be read by the host and are defined as follows:

| D7    | D6   | D5 D4 D3 D2 D1 D0                                                                                                                                                           |                 |                 |                 |                  |                 |  |  |

|-------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----------------|-----------------|------------------|-----------------|--|--|

| Х     | nWTG | nHS3                                                                                                                                                                        | nHS2            | nHS1            | nHS0            | nDS1             | nDS0            |  |  |

| Bit 7 |      | This bit shall be ignored by the host. Please see <b>Appendix B: Card Information Structure</b> of this document for a discussion of the considerations involving this bit. |                 |                 |                 |                  |                 |  |  |

| Bit 6 | nWTG | This bit is cleared while a write operation is in progress, otherwise, it is set.                                                                                           |                 |                 |                 |                  |                 |  |  |

|       |      | When the bit is c                                                                                                                                                           | leared the host | should not alte | r the Vpp or Vo | c supply voltage | es to the card. |  |  |

Table 4-12: Drive Address Register

Refer to the *ANSI ATA Standard* for description of the bits which are described in this register except where the *ANSI ATA Standard* conflicts with the descriptions provided above.

Note: This register is obsolete in some ANSI ATA Standards.

## 4.2.13 Duplicate Data, Error and Feature Registers

The address space occupied by the Data register overlaps with space occupied by the Error and Feature registers. The table below describes the combinations of Data register access and Error or Feature register accesses. The table is provided here to assist in understanding the overlapped Data register and Error or Feature register rather than to attempt to define general PC Card word and byte access modes and operations. See the *PC Card Standard* for definitions of the Card Accessing Modes for I/O and Memory cycles. These cycles are also summarized in Section *2.2 Differences Between PC Card ATA and ATA*.

| Table 4-13: | Duplicate Data | Register |

|-------------|----------------|----------|

|-------------|----------------|----------|

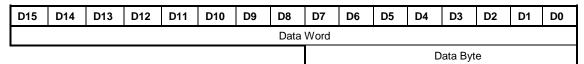

| D15                | D14       | D13 | D12 | D11 | D10 | D9 | D8 | D7 | D6     | D5      | D4     | D3       | D2 | D1 | D0 |

|--------------------|-----------|-----|-----|-----|-----|----|----|----|--------|---------|--------|----------|----|----|----|

|                    | Data Word |     |     |     |     |    |    |    |        |         |        |          |    |    |    |

| Odd Data Byte Only |           |     |     |     |     |    |    |    | Even o | r Even- | Odd Da | ita Byte |    |    |    |

Because of the overlapped registers, access to the Error or Feature registers at 1F1H, 171H and offset 1H are not possible when word accesses are performed, i.e., with **CE1#** and **CE2#** both asserted. The Duplicate Registers at relative addresses 8H, 9H and 0DH have no restrictions on the operations which can be performed by the socket.

| Data Register            | CE2# | CE1# | A0 | Offset  | Data Bus |

|--------------------------|------|------|----|---------|----------|

| Word Data register       | L    | L    | L  | 0н, 8н  | D15-D0   |

| Word Data register       | L    | L    | Н  | 1н, 9н  | D15-D0   |

| Even Byte Data register  | Н    | L    | L  | 0н,8н   | D7-D0    |

| Odd Byte Data register   | Н    | L    | Н  | 9н      | D7-D0    |

| Odd Byte Data register   | L    | Н    | Х  | 8н, 9н  | D15-D8   |

| Error / Feature Register | Н    | L    | Н  | 1н, 0Dн | D7-D0    |

| Error / Feature Register | L    | Н    | Х  | 0н, 1н  | D15-D8   |

| Error / Feature Register | L    | L    | Х  | 0C, 0Dн | D15-D8   |

#### Table 4-14: Access to Data, Error and Feature Registers Including Duplicate Registers

NOTES:

1. The Data register at 0H is accessed with both CE1# and CE2# asserted as a word register on the combined Odd Data Bus and Even Data Bus (D[15::0]). This register may also be accessed by a pair of byte accesses to the offset 0H with CE1# asserted and CE2# negated. Word accesses at odd address N+1 is the same as a word access at address N, however, word accesses at odd addresses are illegal for I/O accesses. Note that the address space of this word register overlaps the address space of the Error and Feature byte-wide registers which are located at offset 1H. When accessed twice as byte register with CE1# asserted, the first byte to be accessed is the Even byte of the Word and the second byte accessed is the Odd byte of the equivalent Word access.

A byte access to address 0H with **CE1#** negated and **CE2#** asserted accesses the Error (read) or Feature (write) register.

2. The registers located at offsets 8H, 9H and 0DH are non-overlapping duplicates of the registers at offsets 0 and 1.

Register 8H is equivalent to register 0H, while register 9H accesses only the Odd byte of the Data register. Therefore, if the registers are byte accessed in the order 9H then 8H the data will be transferred Odd byte then Even byte. Repeated byte accesses to register 8H or 0H will access consecutive (even then odd) bytes from the data buffer. Repeated word accesses to register 8H, 9H or 0H will access consecutive words from the data buffer. Repeated byte accesses to register 9H are not supported. However, repeated alternating byte accesses to registers 8H then 9H will access consecutive (even then odd) bytes from the data buffer. Byte accesses to register 9H access only the odd byte of the data word.

3. Memory accesses to even addresses at offsets between 400H and 7FFH access register 8H. Accesses to odd addresses at offsets between 400H and 7FFH access register 9H. This 1 Kbyte memory window to the Data register is provided so that hosts can perform memory to memory block moves to the Data register when the register lies in memory space. This entire window accesses the Data register FIFO and does not directly address the data buffer within the card. Some hosts, such as the 80x86 processors, increment both the source and destination addresses when executing the memory to memory block move instruction. Some PC Card socket adapters also have auto incrementing address logic embedded within them. This address window allows these hosts and adapters to function efficiently.

## 4.3 ATA Specific Register Mapping

## 4.3.1 I/O Mapped Addressing

The Primary I/O, Secondary I/O, and Contiguous I/O address maps are shown in Table 4-15: I/O Mapped Addressing.

The contiguous I/O mapping mode requires that the system decode a contiguous block of at least 16 I/O registers to uniquely select the card.

| REG# | Primary | Secondary | Contiguous | IORD# =0         | IOWR# =0          | Note |

|------|---------|-----------|------------|------------------|-------------------|------|

|      | A[9::0] | A[9::0]   | A[3::0]    |                  |                   |      |

| L    | 1F0н    | 170н      | Он         | Even Read Data   | Even Write Data   | 1    |

| L    | 1F1н    | 171н      | 1н         | Error Register   | Feature           | 2    |

| L    | 1F2н    | 172н      | 2н         | Sector Count     | Sector Count      |      |

| L    | 1F3н    | 173н      | 3H         | Sector Number    | Sector Number     |      |

| L    | 1F4н    | 174н      | 4H         | Cylinder Low     | Cylinder Low      |      |

| L    | 1F5н    | 175н      | 5н         | Cylinder High    | Cylinder High     |      |

| L    | 1F6н    | 176н      | 6H         | Drive/Head       | Drive/Head        |      |

| L    | 1F7н    | 177н      | 7н         | Status           | Command           |      |

| L    |         |           | 8н         | Duplicate        | Duplicate         | 1,3  |

|      |         |           |            | Even Read Data   | Even Write Data   |      |

| L    |         |           | 9н         | Duplicate        | Duplicate         | 1,3  |

|      |         |           |            | Odd Read Data    | Odd Write Data    |      |

| L    |         |           | 0DH        | Duplicate Error  | Duplicate Feature | 3    |

| L    | 3F6н    | 376н      | 0Ен        | Alternate Status | Device Control    |      |

| L    | 3F7н    | 377н      | 0FH        | Drive Address    | Reserved          | 4    |

#### Table 4-15: I/O Mapped Addressing

NOTES: